## **StarRC**

# Golden Signoff Parasitic Extraction

#### Overview

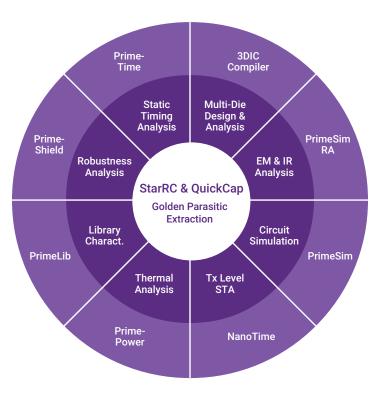

Synopsys StarRC™, the Gold standard parasitic extraction solution, is a key component of the Synopsys Digital Design and the Synopsys Custom Design Families. Synopsys StarRC provides a silicon-accurate and high-performance extraction solution for SoC, custom digital, analog/mixed-signal, memory and 3DIC designs. The Synopsys StarRC solution offers modeling of physical effects for advanced process technologies, including FinFET technologies at 16nm, 14nm, 10nm, 7nm, 5nm, 3nm and beyond. Its seamless integration with industry standard digital and custom implementation systems, physical verification timing, signal integrity, power, thermal and circuit simulation flows deliver unmatched ease-of-use and productivity to speed design closure and signoff verification.

Figure 1: Synopsys StarRC is tightly integrated in the design analysis ecosystem

#### Synopsys StarRC Solution

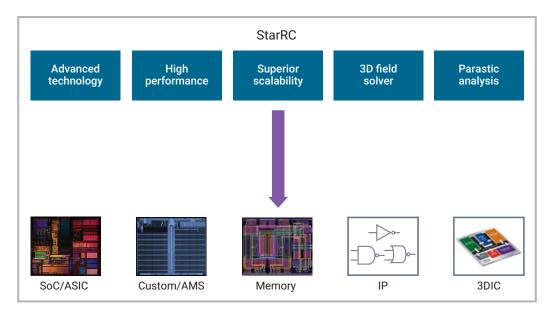

Semiconductor process technology has been continually scaling down for the past four decades and the trend continues. Shrinking process geometries, combined with the use of new device structures like FinFETs and an increasing number of metal layers at each new process node, are introducing millions of new parasitic effects in designs. In addition, soaring design sizes and complexities are increasing the sensitivity of circuits to parasitics due to the increasing impact on signal timing, noise, and power. To ensure a successful silicon design and meet tapeout schedules, IC designers need an advanced parasitic extraction solution that delivers signoff accuracy and increased designer productivity. Furthermore, they need a solution that is versatile enough to manage the full design spectrum from custom digital, analog/mixed-signal (AMS) to full-chip memory and SoC designs. Synopsys' StarRC is the proven high-accuracy and high-performance parasitic extraction solution for digital and custom IC implementation and signoff verification (Figure 2). Trusted by hundreds of semiconductor companies and used in thousands of production designs, Synopsys StarRC provides subfemtofarad-accurate technology for design at advanced process technologies. It achieves its high accuracy by performing detailed modeling of device and interconnect parasitic effects in nanometer process technologies. The advanced modeling and accuracy is complemented with the embedded Rapid3D™ field solver technology for circuits that require even higher accuracy. Synopsys StarRC delivers industry-leading performance and capacity for users' gate-level and transistor-level extraction needs. Synopsys StarRC's multicore distributed processing technology delivers excellent scalability for efficient utilization of available hardware, and its simultaneous multi-corner extraction (SMC) feature allows the increasing number of extraction corners required for analysis to be processed within a single run with significantly reduced runtime and disk usage. Its seamless integrations with Synopsys IC Compiler™ II place-androute solution, Synopsys Fusion Compiler™ RTL-to-GDSII solution, Synopsys PrimeTime® golden static timing analysis (STA) solution, Synopsys Custom Compiler™ design environment, Synopsys IC Validator™ physical verification solution, Synopsys PrimeSim™ circuit simulation technologies, and other third-party implementation and signoff tools enables users to significantly accelerate their design implementation and verification.

Figure 2: Synopsys StarRC provides a parasitic extraction solution for gate-level and transistor-level digital and custom IC designs

#### **Benefits**

- Foundry gold standard for extraction accuracy with broadest qualification and adoption

- Leader in advanced modeling, including FinFET and color-aware multi-patterning at 10nm/7nm/5nm/3nm and beyond.

- High performance and capacity for gate and transistor-level extraction, enabled by multi-core distributed processing and simultaneous multi-corner extraction

- Tightly integrated with industry leading Synopsys IC Compiler II and Synopsys PrimeTime solutions for faster full-flow ECO turn-around time

- · Unified Rapid3D fast field solver for critical net, IP, and custom circuit extraction

- · Advanced netlist reduction features for faster simulation turn-around time

- · Inductance extraction for high frequency digital RLC clock net analysis

- · 3DIC extraction solution for interposer and stacked die technologies

- Integration with Synopsys IC Validator physical verification solution, Synopsys PrimeSim circuit simulation technologies,

Synopsys Custom Compiler design environment and other third-party implementation and custom design solutions for increased designer productivity

#### **Advanced Process Modeling**

Increasing process variation and new parasitic effects introduced at each new technology node are significantly increasing design challenges. Process technologies at 40nm and 28nm elevated a variety of physical effects once considered secondary to primary factors affecting circuit behavior, risking performance degradation, silicon failure and lower yields if not accurately modeled. Some typical process modeling capabilities offered by Synopsys StarRC include litho-aware extraction and chemical mechanical polishing (CMP)-based thickness variation extraction, as well as modeling of micro-loading effects and low K dielectric damage. For transistor-level circuit modeling, gate-to-contact capacitance, gate-to-diffusion capacitance, and contact etch effects are some of the device parasitics which are accurately modeled by Synopsys StarRC for increased signoff integrity, with the additional benefit of being modeled in context with the layout environment for even higher accuracy. In addition, striking changes in process technology, like double-patterning lithography at 20nm, 16nm/14nm FinFET transistor architecture, 10nm/7nm multi-patterning lithography, and further FinFET architecture enhancements at 10nm and 7nm are requiring consideration of a host of completely new and complex effects with even more ramifications on extraction, timing analysis and design robustness. More than ever, the accuracy of parasitic modeling and extraction results is contributing to overall design integrity.

#### 20nm Double Patterning Technology (DPT)

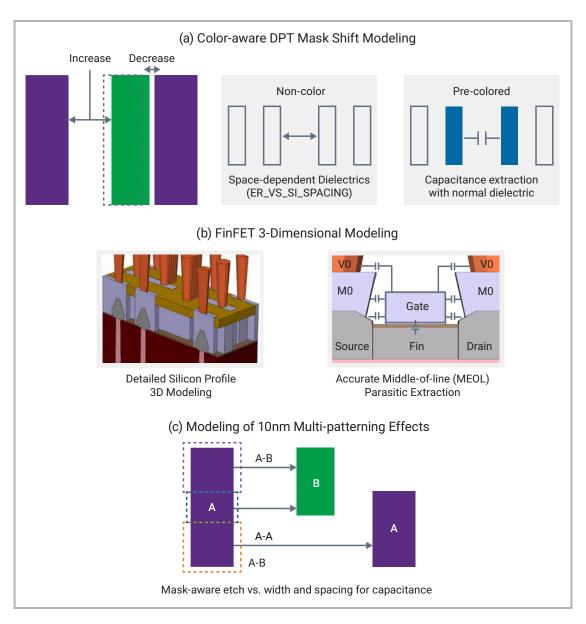

Modeling At 20nm, significant capacitance variation is introduced by double-patterning, a fabrication strategy where metal lines on a single layer are created in two separate masking steps to achieve finer metal pitch. Misalignment between the patterns causes coupling capacitance between adjacent metal lines to increase in one direction and to decrease in another (Figure 2a). Synopsys StarRC models these capacitance variations with a novel modeling technique that ensures that these effects are accounted for accurately while preserving the existing signoff flows.

## FinFET Modeling

Even more radical changes are introduced by 16nm/14nm FinFET transistor architecture. In contrast with planar transistors, FinFETs are able to achieve better control over the source-drain channel because the gate encloses the channel on three sides, resulting in higher mobility, greater drive strength, lower switching currents and lower leakage currents. But this multi-gate, non-planar architecture also introduces more complex co-vertical geometries and many new capacitive elements that must be accurately extracted due to their impact on circuit performance. Synopsys StarRC uses a uniquely detailed FinFET physical profile derived from Synopsys QuickCap® NX's field solver technology for 3D modeling of layout-dependent middle-end-ofline (MEOL) parasitic effects (Figure 2b) for increased accuracy. At 10nm and 7nm, new materials and geometries are being introduced to FinFETs to reduce operating voltage while improving transistor performance. Due to its advanced modeling solution, Synopsys StarRC is the extraction tool of choice for foundries and IP developers to model new parasitic effects and ensure proper characterization of FinFET devices.

Figure 3: Synopsys StarRC's advanced 20nm DPT, 16nm/14nm FinFET, and 10nm modeling for signoff accuracy

## 10nm/7nm Multi-patterning Modeling

At 10nm and 7nm, where even finer metal pitch geometries must be resolved than at 20nm, multi-patterning of three or more mask layers is used. This requires an even more complex capacitance variation model which requires properly identifying each conductor's printed mask layer, or "color", as well as accounting for adjacent metal line width and spacing effects (Figure 3). Synopsys StarRC's 10nm and 7nm extraction solutions are fully color-aware and include updated Interconnect Technology Format (ITF) constructs to support all etch effects associated with a range of foundry multi-patterning lithography strategies for 10nm and 7nm.

#### 5nm/4nm/3nm node Modeling

Synopsys StarRC is fully certified by all major foundries for all process flavors of 5nm, 4nm & 3nm including Gate All Around devices. These advanced technology nodes require StarRC to support via location dependent MOS gate resistance adjustment, MOL layer recess modeling and 5-dimensional LEE modeling. At lower single digit nanometer nodes, Synopsys StarRC handle multiple conductors with different resistance profiles but with same capacitance profile efficiently to ensure superior TAT. Scaling of conductors increases resistance dramatically in lower conductors and Synopsys StarRC special fracturing, node generation similar to Synopsys QuickCap NX and via location aware resistance distribution enables accurate post layout timing and reliability analysis.

#### 3DIC Modeling

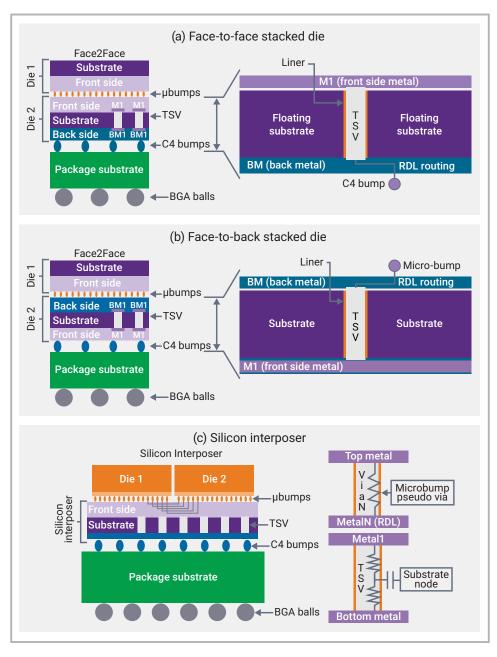

Synopsys StarRC also supports extraction for stacked die and silicon interposer 3DIC technologies (Figure 4). Synopsys StarRC extracts through-silicon vias (TSV) and substrates, TSV-TSV capacitive coupling, silicon interposers, micro-bump structures, and routing layers on each die. StarRC supports modeling substrates as either floating or grounded. Synopsys StarRC's extraction and modeling of through-silicon vias and substrates through Synopsys' Interconnect Technology Format (ITF) has been qualified by several major foundries and is found in their 3DIC reference flows.

Figure 4: 3DIC stacked die and interposer profiles example

#### Multi-Core Distributed Processing

Multi-core processor hardware has become common due to the widespread need for higher productivity. A large majority of design jobs are run on compute farms consisting of multi-core machines, and IC designers seek design tools that harness the full potential of their hardware network. Synopsys StarRC's multi-core technology works seamlessly with popular commercial grid computing management software to maximize efficiency across multi-core processors, as well as multiprocessor compute farms, to take full advantage of available hardware. Synopsys StarRC offers high performance per CPU core, with 12X scalability on 16 cores and over 20X on 32 cores. In addition, Synopsys StarRC multi-core distributed processing provides easy-to-setup compute resource allocation, automated design partitioning to multiple cores, balanced load sharing, and automatic failure recovery for a superior fault-tolerant server environment

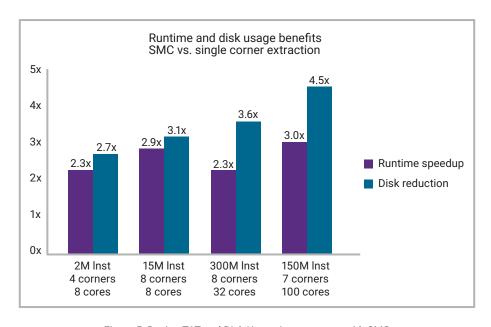

#### Simultaneous Multi-Corner Extraction

The increase in process variation and decrease in process geometries found in technology nodes at 20nm and below have resulted in a significant growth in the number of extraction corners requiring analysis. This in turn is having a significant impact on the efficiency of designers. To mitigate the increased turnaround time (TAT) caused by this rise in extraction corners, Synopsys StarRC offers ultra-scalable simultaneous multi-corner extraction, where in all extraction corners can be analyzed within a single run. For designers traditionally executing multiple extraction runs in parallel, runtime speedup of up to 3X is achieved when using SMC and aggregating hardware resources within a single run. Those with resource—limited environments running serial extractions will see even greater TAT benefits when comparing total extraction runtime to a single SMC run. Runtime speedup of 2-3X can be seen across designs ranging in size from 2M to 300M instances. Synopsys StarRC's ultra-scalable multi-core technology enables the use of over 100 CPU cores for faster speed up on large designs. Disk usage with SMC is also significantly reduced, typically by 75% or more depending upon the number of corners extracted. Synopsys StarRC's SMC feature is available for both gate-level and transistor-level extraction.

Figure 5: Design TAT and Disk Usage Improvement with SMC

#### **Fast ECO Extraction**

The ECO timing closure cycle has become a significant TAT issue for designers. Final design optimization which may affect only a small portion of a chip introduces lengthy delays in tapeout schedules. In order to minimize the impact of these changes in extraction, Synopsys StarRC fast ECO extraction allows designers to extract only those nets affected by ECO changes versus re-analyzing an entire design. Synopsys StarRC fast ECO extraction achieves up to 5X faster extraction TAT while maintaining the same signoff accuracy as full extraction. Synopsys StarRC is also tightly integrated with Synopsys PrimeTime STA solution and Synopsys Fusion Compiler RTL-to-GDSII solution, allowing designers to achieve faster ECO turn-around time across their entire digital implementation and signoff flow. Synopsys Fusion Compiler directly updates Synopsys StarRC with ECO database changes for faster identification of ECO affected nets. Synopsys PrimeTime also directly reads Golden Parasitic Data (GPD) from Synopsys StarRC, eliminating the need for separate SPEF netlists to be generated by Synopsys StarRC and input into Synopsys PrimeTime.

#### Inductance Extraction for High Frequency Clock Nets

Inductance effects are becoming increasingly important to model for high frequency, low resistance nets, such as those for high-performance clocks routed on upper layer metals. Inductance effects on clock nets include steeper edge rates, push out delays, and voltage undershoot and overshoot. Synopsys StarRC's inductance extraction feature models the inductance on clock nets with pre-defined power/ ground net shielding and includes the inductance values in Detailed Standard Parasitic Format (DSPF) netlists for simulation analysis. Inductance extraction is invoked from the same Synopsys StarRC interface as RC extraction and uses standard foundry technology files for input. The inductance values extracted with this feature correlate within 10% to FastHenry, ensuring high accuracy as well as high productivity

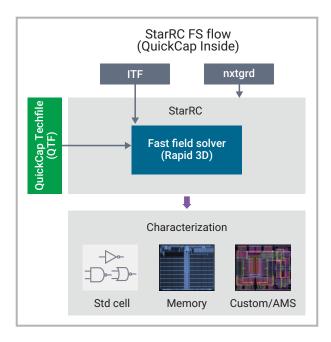

#### High Accuracy Fast Field Solver Extraction

For timing sensitive implementations such as clock networks, memories, analog/ mixed signal/RF, high-speed digital, standard cells and other IP designs, accuracy is a non-negotiable design criterion. Designers of such critical IP and circuits generally require field solver level accuracy as well as fast turnaround time. Synopsys StarRC offers integrated fast field solver extraction, Rapid3D with merged Synopsys QuickCap NX technology, for industry's highest accuracy 3D extraction. It incorporates the latest advancements in field solver algorithms to deliver highest performing 3D extraction while providing golden accuracy. The embedded Rapid3D technology complements Synopsys StarRC's primary extraction engine for 3-dimensional self- and coupling capacitance extraction of critical circuits. Within the single Synopsys StarRC environment, users can supply a list of nets that need the highest level of accuracy for capacitance extraction. The tool not only extracts the nets in the regular flow, but it also creates a subset of the design based on the user-specified nets to be extracted using the field solver technology. A merged netlist is generated including the higher accuracy field solver extracted nets (Figure 5)

## Synopsys PrimeSim Circuit Simulator and Synopsys PrimeSim Reliability Analysis Integration

Post-layout simulation runtimes are increasing 2-4X with every new process generation. More accurate and efficient parasitic extraction is needed to accelerate simulation and meet tapeout schedules. Synopsys StarRC offers seamless integration with SynopsysPrimeSim circuit simulator and a wide range of innovative features to boost simulation performance and capacity while preserving signoff accuracy. Synopsys StarRC's exclusive interface with PrimeSim includes active node extraction, post layout acceleration with hierarchical back-annotation, and power network optimization. The integration between the two tools enables over 10X simulation performance speed-up for custom IC and memory designs.

Need for low defect rates and long-term reliability of the various Integrated circuits added another layer of complexity to the design closure process. Synopsys PrimeSim Reliability Analysis solution offers a comprehensive solution for electromigration/IR drop analysis, high sigma Monte Carlo, MOS aging, and analog fault simulation. Synopsys StarRC's unique ability to understand the design topology allows it to extract conductor and via elements of any analog design in accordance with the Synopsys PrimeSim RA requirements to support robustness analysis (missing vias, static IR etc.,), reliability analysis (Electromigration, self-heating analysis, multi-mode analysis), and thermal analysis.

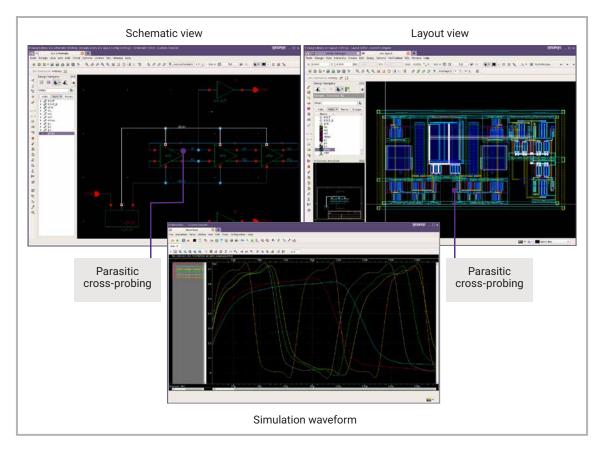

#### **Custom AMS Design Platform Integration**

Synopsys StarRC is integrated with the Synopsys Custom Compiler environment and with Cadence®Virtuoso® Analog Design Environment (ADE) for custom AMS and custom digital designs. Synopsys StarRC and Synopsys Custom Compiler offer users the unique benefits of an OpenAccess interface combined with the ease-of-use of the Synopsys CustomDesign Family solutions using a common data flow. Synopsys Custom Compiler users can measure parasitics with Synopsys StarRC directly from the layout canvas while they work. This shortens the time to design closure by catching parasitic issues early during layout. Synopsys Custom Compiler users can also use "partial layout extraction" flow with Synopsys StarRC and Synopsys IC Validator, which enables designers perform early parasitic simulations before the layout is complete. For the Virtuoso environment, Synopsys StarRC generates OpenAccess or Cadence DFII database parasitic views for netlisting and simulation, compatible with common netlisting interfaces used within ADE. Synopsys StarRC offers full parasitic probing capabilities within the parasitic view or within the matching schematic view (Figure 6). The parasitic prober allows users to interactively observe point-to-point resistance, total net capacitance, net-to-net coupling capacitance and cross-probing between schematic and parasitic views. It also provides the ability to output probed parasitics to an ASCII report file, and to annotate parasitic view total capacitance values to an associated schematic view.

Figure 6: Synopsys StarRC integrated fast field solver extraction offers high-accuracy extraction for critical IP within a single extraction environment

## **Process Modeling**

- 10nm/7nm color-aware multi-patterning

- · Via coverage resistance variation modeling

- · FinFET 3D modeling

- · Color-aware double patterning

- · Trench contact modeling

- Inductance extraction for high frequency clock nets

- Embedded 3D field solver

- · 3DIC, Silicon Interposer TSV modeling

- · Via etch modeling

- · Width- and spacing-dependent thickness variation

- Density-based thickness variation

- Width- and spacing-dependent resistance per square (RPSQ) variation

- · RPSQ variation as function of silicon width

- · Nonlinear RPSQ variation

- · Trapezoidal polygon support

- · Copper interconnect, local interconnect modeling

- · Low-K dielectric, silicon on insulator (SOI) modeling

- · Conformal dielectric process support

- · Via cap extraction

- · Layer etch effects

- · Temperature-dependent resistance modeling for conducting layers and vias

- · Support of background dielectric

- · Nonlinear via resistance modeling

- 45-degree routing support

- · Support of multiple inter-layer and intralayer dielectric

- · Support for co-vertical conductors

- · Support for non-planarized metal

#### Productivity and Ease-of-use

- · Multi-core distributed processing

- · Simultaneous multi-corner extraction

- Fast ECO extraction for ECO TAT reduction

- Clock inductance extraction

- Integration with Synopsys PrimeTime and Synopsys Fusion Compiler for ECO TAT reduction

- Synopsys PrimeSim circuit simulation integration

- Custom layout environment integration

- · Physical implementation interface (GDSII, LEF/DEF, NDM)

- · Golden Parasitic Data (GPD) interface to Synopsys PrimeTime

- · Virtual metal fill for accurate design capacitance

- Metal fill re-use for ECO TAT reduction

- · Hierarchical layout-versus-schematic (LVS) and advanced device parameter ADP extraction flow

- Active node extraction

- · Selective device parasitic handling

- · Flexible parasitic reduction

- Automated power net extraction optimization (TARGET\_PWRA)

- Transparent simulation setup

- · License queuing

- · User-control reduction of parasitic netlists

- · Advanced reduction features for simulation productivity

Figure 7: Synopsys StarRC integration with custom design environments, such as Synopsys Custom Complier

## **Specifications**

File Format Support

Synopsys StarRC supports the following industry standard formats and interfaces:

Layout data in: GDSII, LEF/DEF, Milkyway, NDM, Synopsys IC Compiler II, Synopsys Fusion Compiler, Synopsys IC Validator, Cadence®Virtuoso® and Siemens EDA® Calibre®

Output formats: GPD, SPEF, DSPF, SPICE, OA view, Parameterized Spice, STAR and Extractive view.

#### Platform/OS

- IBM® RS/6000® AIX® (64)

- x86 Red Hat® Enterprise Linux® (64)

- x86 SUSE® Linux (64)